### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 8, August 2016

### A Novel Three-Phase Hybrid Multilevel Inverter Using Switched Capacitor Units for Industrial Applications

Y.Nagendra, R.Kumara Swamy

Assistant Professor, Department of Electrical & Electronics Engineering, Narsimha Reddy Engineering College, Maisammaguda, Rangareddy (Dt), Telangana, India.

Assistant Professor, Department of Electrical & Electronics Engineering, Narsimha Reddy Engineering College, Maisammaguda, Rangareddy (Dt), Telangana, India.

**ABSTRACT:** Multilevel power converter structure has been introduced as an alternative in high power and medium voltage situations. A multilevel converter not only achieves high power ratings, but also improves the performance of the whole system in terms of harmonics, dv/dt stresses, and stresses in the bearings of a motor. Moreover the advantages like high quality power output, low switching losses, low electro-magnetic interference (EMI) and high output voltage made multilevel inverter as a powerful solution in converter topology. In this paper two new topologies have been proposed for multilevel inverters. The proposed topologies consist of a combination of the conventional series and the switched capacitor inverter units. The proposed method introduces 17, 25 levels and three phase 25level Inverter, With the use of high level inverter, resolution is increase and also the harmonics is highly reduced. The simulation results are presented by using Matlab/Simulink software.

KEYWORDS: Multilevel inverter, series inverters, series parallel connection, switched capacitor

#### I. INTRODUCTION

Multilevel inverters have been under research and development for more than three decades and have found successful industrial applications. However, this is still a technology under development, and many new contributions and new commercial topologies have been

reported in the last few years. Large electric drives and utility applications require advanced power electronics converter to meet the high power demands. As a result, multilevel power converter structure has been introduced as an alternative in high power and medium voltage situations [1]. A multilevel converter not only achieves high power ratings, but also improves the performance of the whole system in terms of harmonics, dv/dt stresses, and stresses in the bearings of a motor. Several multilevel converter topologies have been also developed i) diode clamped, ii) flying capacitors, and iii) cascaded or H-bridge. Referring to the literature reviews, the cascaded multilevel inverter (CMI) with separated DC sources is clearly the most feasible topology for use as a power converter for medium & high power applications due to their modularization and extensibility [2].

The elementary concept of a multilevel converter to achieve higher power is to use a series of power semiconductor switches with several lower voltage dc sources to perform the power conversion by synthesizing a staircase voltage waveform [3-10]. Capacitors, batteries, and renewable energy voltage sources can be used as the multiple dc voltage sources. The commutation of the power switches aggregate these multiple dc sources in order to achieve high voltage at the output however, the rated voltage of the power semiconductor switches depends only upon the rating of the dc voltage sources to which they are connected.

A multilevel converter has several advantages over a conventional two-level converter that uses high switching frequency Pulse Width Modulation (PWM). Staircase waveform quality: Multilevel converters not only can generate the output voltages with very low distortion, but also can reduce the dv/dt stresses; therefore electromagnetic compatibility (EMC) problems can be reduced [11], [12].

Copyright to IJAREEIE

DOI:10.15662/IJAREEIE.2016.0508076

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 8, August 2016

The proposed topologies have a modular structure and can benefit the advantages of the series multilevel inverters [13]. The fundamental switching method is used in this investigation. In addition, to produce all voltage levels at the output (even and odd), a new algorithm for the determination of the magnitude of the isolated dc voltage sources is proposed. Finally, the loss calculation is done, and the performance of the proposed topologies is verified by simulation results of single-phase 25- and 17-level inverters.

#### II.PROPOSED SWITCHED CAPACITOR TOPOLOGY

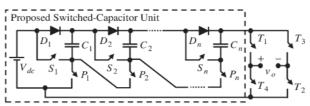

Fig.1. shows the proposed switched capacitor unit. This topology is yield from series combination of several basic units. In this figure, the switches Si (i=1, 2, n) connect the capacitors in series, and the switches  $P_i$  connect the capacitors in parallel with the dc voltage sources. To produce zero and negative voltage levels, an H-bridge has been used at the output. The blocked voltage by each switch in Fig.1. is  $V_{\rm dc}$ .

Fig.1. Proposed Switched Capacitor Unit.

Thus, the proposed switched capacitor unit is also proper for a high frequency application that is not the aim of this paper. The other advantage of the proposed topology is the boosting ability of the input dc voltage without using any transformer. This feature reduces the size and cost of the system and increases its efficiency. The maximum numbers of output voltage levels (N-step), required insulated-gate bipolar transistors (IGBTs) (NIGBT), and diodes (N-diode) for the proposed topology shown in 3.3 are calculated by the following equations, respectively,

$$N_{step} = 2n + 3 \tag{1}$$

$$N_{IGBT} = 2n + 4 \tag{2}$$

$$N_{diode} = n (3)$$

Where n is the number of capacitors. The maximum output voltage that can be produced  $(V_{o,max})$  is equal to

$$V_{0,max} = (n+1)V_{dc} (4)$$

In order to reduce the capacitor voltage drop during the series connection, the pulse width-modulation switching pattern can be used between the  $i^{th}$  and  $(i+1)^{th}$  consecutive voltage levels  $(i=0,\,1,\,2,\,n)$ , which, in turn, will increase the losses. On the other hand, more capacitors are needed to produce more levels at the output. Greater number of series capacitors increases their voltage drop. Thus, generating desirable voltage waveform without using of filtering elements will be difficult and requires more complex switching schemes. To produce greater number of voltage levels at the output and reduce the capacitor voltage drop, several units shown in Fig.1 can be used in series. In this condition, the first unit, the second unit, and the  $k^{th}$  unit have  $n_1,\,n_2,$  and  $n_k$  capacitors and dc voltage sources with magnitudes of  $V_1,\,V_2,$  and  $V_k,$  respectively.

### International Journal of Advanced Research in Electrical, **Electronics and Instrumentation Engineering**

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 8, August 2016

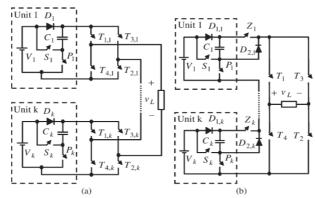

Fig.2. (A) First Proposed Topology. (B) Second Proposed Topology.

The general form of the equations that show the number of voltage levels and the number of IGBTs can be expressed as follows:

$$N_{step} = a \left[ \prod_{j=1}^{k} (bn_j + c) \right] + d$$

(5)

$$N_{IGBT} = 2 \left( \sum_{j=1}^{k} n_j \right) + ek + f$$

(6)

$$N_{IGBT} = 2\left(\sum_{i=1}^{k} n_i\right) + ek + f \tag{6}$$

Where a, b, c, d, e, and fare the integer numbers that depend on the unit connection order. In order to produce the maximum number of voltage levels at the output with using a specified number of IGBTs, (6) can be rewritten as follows:

$$N_{IGBT} = 2(n_1 + n_2 + \dots + n_k) + ek + f = cte$$

(7)

$$n_1 + n_2 + \dots + n_k = \frac{N_{IGBT} - ek - f}{2} = cte$$

(8)

Considering (5) and (8), the number of voltage levels in (5) will be maximum when the following condition is satisfied

$$n_1 = n_2 = \dots = n_k = n \tag{9}$$

From (8)–(10), Nstep is obtained as follows

$$N_{step} = a(bn + c)^{\frac{N_{IGBT} - f}{2n + e}} + d \qquad (10)$$

Equation (10) will be maximum when nets its minimum value. Thus, the proposed topologies produce the maximum number of voltage levels at the output form=1. This result is independent of the units' connection order. The proposed topologies have been presented in the next sections with considering n=1.

#### A. First Proposed Topology

Fig.2.(a) shows the first proposed topology. In this topology, the switched capacitor units have been connected in series by using H-bridges. Each unit can only produce positive voltage levels. The H-bridge produces zero and negative voltage levels. There are a lot of ways to determine the magnitude of the dc voltage sources. Some of these algorithms are not able to produce all voltage levels at the output, and some of them produce repetitive voltage levels. In order to prevent the mentioned problems and produce the maximum number of voltage levels, the magnitude of the dc voltage sources in the  $j_{th}$  unit can be as follows:

$$V_i = (5^{j-1})V_1 \tag{11}$$

Voltage and current ratings of the switches in a multilevel inverter play important roles in the total cost of the inverter. In all topologies, the currents of all switches are equal to the rated current of the load. This is, however, not the case for the voltage. Hence, there is a need for a criterion to evaluate the multilevel inverter from the viewpoint of blocked voltage by power switches and the total cost of system. This criterion is captioned as "standing voltage". The standing voltage is equal to the sum of all blocked voltages by power switches in a converter. The standing voltage of the switches is equal to the sum of the blocked voltages by switches S and P and the H-bridge switches for all units.

### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 8, August 2016

#### B. Second Proposed Topology

Fig.2. (b) shows the second proposed topology. In this topology, each unit is bypassed when the switch  $P_j$  and the diode  $D_{2,j}$  are on and the switch  $Z_j$  is off. When the switch  $Z_j$  is on, the diode  $D_{2,j}$  becomes reverse biased. Thus, the diode  $D_{2,j}$  prevents the backward current flowing during the unit bypassing when an inductive load is used at the output. In other words, the second proposed topology can produce the desirable voltage waveforms for resistive loads. On the other hand, by replacing the diode  $D_{2,j}$  with a power electronic switch, the second proposed topology can be used for resistive-inductive loads. The magnitude of the dc voltage sources and the number of voltage levels can be calculated as follows:

$$V_j = (3^{j-1})V_1 (12)$$

The number of voltage levels ( $N_{\text{step}}$ ), the number of required IGBTs (NIGBT), the number of diodes ( $N_{\text{diode}}$ ), the maximum output voltage ( $V_{\text{o}}$ , max), the standing voltage of the switches ( $V_{\text{st}}$  and), the number of dc voltage sources ( $N_{\text{dc}}$ ), and the variety of the dc voltage source magnitude ( $N_{\text{variety}}$ ) can b calculated for the first and second proposed topologies, as shown in Table I.

#### III. COMPARISON OF THE PROPOSED TOPOLOGIE SWITH OTHER CONVENTIONAL TOPOLOGIES

In this section, the first proposed topology has been compared with three main topologies of multilevel inverters, namely, the diode-clamped multilevel one, capacitor

Table I Calculation of Different Parameters of the Proposed Topologies

| Parameter            | Proposed Topology                                                                                |                                                            |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|

|                      | First                                                                                            | Second                                                     |  |  |  |

| N <sub>step</sub>    | 5 <sup>k</sup>                                                                                   | (2X3 <sup>k</sup> )-1                                      |  |  |  |

| N <sub>IGBT</sub>    | $6^{k}$                                                                                          | 3k+4                                                       |  |  |  |

| N <sub>diode</sub>   | k                                                                                                | 2k                                                         |  |  |  |

| $V_{0,max}$          | $2\sum_{j=1}^{k} V_{j}$                                                                          | $2\sum_{j=1}^{k}V_{j}$                                     |  |  |  |

| V <sub>stand</sub>   | $ \begin{array}{c} 10(1+5+\ldots+5^{k-1})V_1 \\ = 5\left[\frac{5^k-1}{2}\right]V_1 \end{array} $ | $11(1+3++3^{k-1})V_1$ $=11\left[\frac{3^k-1}{2}\right]V_1$ |  |  |  |

| $N_{dc}$             | k                                                                                                | k                                                          |  |  |  |

| N <sub>variety</sub> | k                                                                                                | k                                                          |  |  |  |

Table II Comparison of the First Proposed Topology With The Topologies Presented

| Topologies     | N <sub>step</sub> | N <sub>switch</sub> | $N_{diode}$ | $N_{capacitor}$ | $N_{dc}$ |

|----------------|-------------------|---------------------|-------------|-----------------|----------|

| First topology | 25                | 12                  | 2           | 2               | 2        |

| DCM            | 13                | 24                  | 132         | 12              | 1        |

| CCM            | 13                | 24                  | 0           | 66              | 1        |

| CMM            | 13                | 24                  | 0           | 6               | 1        |

| CBSCM          | 13                | 10                  | 12          | 6               | 1        |

| SCBM           | 13                | 11                  | 3           | 2               | 1        |

| HSSCM          | 13                | 21                  | 4           | 5               | 3        |

Clamped multilevel one, and cascaded multi cell multilevel one. Also, the proposed topology has been compared with a cascade-boost switched capacitor converter multilevel inverter, a switched capacitor boost multilevel inverter, and a

### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 8, August 2016

hybrid-source switched capacitor multilevel inverter [9]. Table II shows the numbers of switches, diodes, capacitors, and voltage levels for the proposed topology and the topologies presented in [9]. Table II proves the advantages of the proposed topology. In order to show the advantages of the proposed topologies in comparison with some recently presented topologies that use isolated dc voltage sources, the proposed topologies have been compared with the cascaded multilevel inverter using bidirectional switches (CMIBS), cascaded multilevel inverter using binary units (CMIBU), optimal topologies for cascaded sub multilevel inverters (OCSMI), cascaded multilevel inverter with reduced number of components for high-voltage applications (CMIHV), multilevel inverter with reduced number of power electronic components (MIRC), and multilevel inverter using switched series/parallel dc voltage sources (MISSP) from different aspects. Fig.3. shows the number of required IGBTs for producing specified voltage levels at the output of the proposed topologies and the topologies presented. As can be seen, the proposed topologies need fewer IGBTs for realized Nstep voltage levels at the output.

#### IV.MATLAB/SIMULINK RESULTS

Here simulation results are presented for (i) Single phase 17-level inverter (ii) single phase 25-level inverter (iii) three phase 25-level inverter

#### Case i: Single Phase 17-level inverter

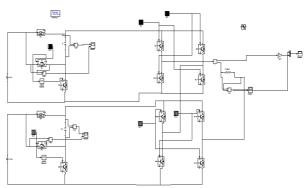

Fig.4.Matlab/Simulink model of 17-level inverter based proposed topology.

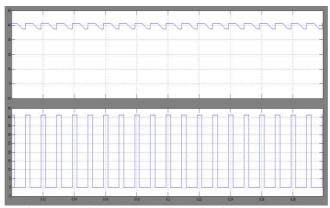

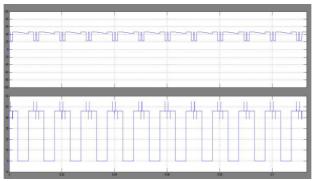

Fig.5. capacitor voltage (Vc1) and switch voltage(S1).

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 8, August 2016

Fig. 6. capacitor voltage(Vc2) and switch voltage(S2).

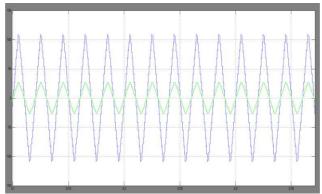

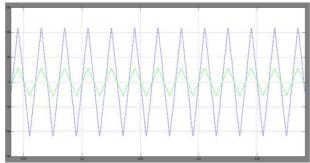

Fig.7. Simulated load voltage and current waveforms for 17-level inverter.

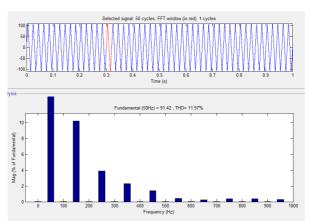

Fig.8.total harmonic distractions for 17 Level inverter.

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 8, August 2016

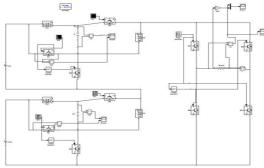

#### Case ii: Matlab circuit of 25-level inverter

Fig.9.Matlab/Simulink model of 25-level inverter based proposed topology.

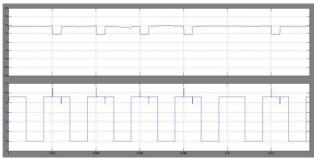

Fig. 10 capacitor voltage (Vc1) and switch voltage (S1).

Fig.11.capacitor voltage (Vc2) and switch voltage (S2).

Fig.12. Simulated load voltage and current waveforms for 25-level inverter. Decisive

Copyright to IJAREEIE DOI:10.15662/IJAREEIE.2016.0508076 7077

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 8, August 2016

Fig.13.total harmonic distractions for 25 Level inverter.

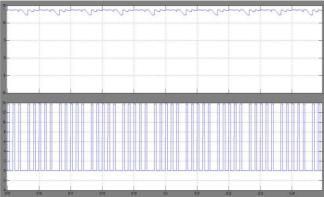

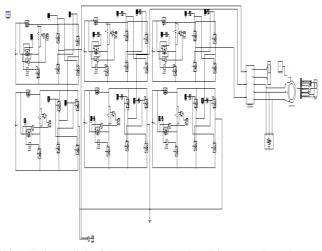

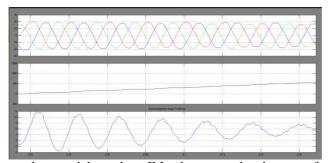

#### Case iii: Three phase 25-level inverter with Induction Motor

Fig.14.Matlab/Simulink Model of three phase 25-level inverter based Proposed Topology

Fig 15. Three Phase voltage and three phase IM voltage, speed and torque for 25-level inverter

#### V. CONCLUSION

The drive system can be used in industries where adjustable speed drives are required to produce output with reduced harmonic content. The simulation results of voltage, current, speed and spectrum are presented. The number of on-off times in one cycle and the conduction intervals offal switches have been calculated as a function of the output voltage

### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 8, August 2016

levels. The proposed topologies reduce the number of switches and isolated dc voltage sources, the variety of the dc voltage source values, and size and cost of the system in comparison with conventional series topologies. The first proposed topology produces a 25-level voltage for all load power factors by using 12 IGBTs, 2 diodes, and 2 isolated dc voltage sources. It is also observed that the proposed topology decreased the number of required power electronic switches compared to a cascaded H-bridge inverter to obtain the same 17 and 25 level output voltage with lower THD.

#### REFERENCES

- [1] K. Bandara, T. Sweet, and J. Ekanayake, "Photovoltaic applications for off-grid electrification using novel multi-level inverter technology with energy storage," Renew. Energy, vol. 37, no. 1, pp. 82–88, Jan. 2012.

- [2] J. Chavarria, D. Biel, F. Guinjoan, C. Meza, and J. J. Negroni, "Energybalance control of PV cascaded multilevel grid-connected inverters under level-shifted and phase-shifted PWMs," IEEE Trans. Ind. Electron., vol. 60, no. 1, pp. 98–111, Jan. 2013.

- [3] N. A. Rahim, K. Chaniago, and J. Selvaraj, "Single-phase seven-level grid-connected inverter for photovoltaic system, "IEEE Trans. Ind. Electron., vol. 58, no. 6, pp. 2435–2443, Jun. 2011.

- [4] A. K. Pandam and Y. Suresh, "Performance of cascaded multilevel inverter by employing single and three-phase transformers, "IET Power Electron., vol. 5, no. 9, pp. 1694–1705, Nov. 2012.

- [5] Y. Hinago and H. Koizumi, "A switched-capacitor inverter using series/ parallel conversion with inductive load," IEEE Trans. Ind. Electron., vol. 59, no. 2, pp. 878–887, Feb. 2012.

- [6] P. Roshankumar, P. P. Rajeevan, K. K.Mathew, J. I. Gopakumar, and L. G. Leon, "A five-level inverter topology with single dc supply by cascading a flying capacitor inverter and an H-bridge," IEEE Trans. Power Electron., vol. 27, no. 8, pp. 3505–3512, Aug. 2012.

- [7] A. K. Sadigh, S. H. Hosseini, M. Sabahi, and G. B. Gharehpetian, "Double flying capacitor multicell converter based on modified phase-shifted pulse width modulation," IEEE Trans. Power Electron., vol. 25, no. 6, pp. 1517–1526, Jun. 2010.

- [8] Y. Ounejjar, K. A. Haddad, and L. A. Gregoire, "Packed U-cells multilevel converter topology: Theoretical study and experimental validation," IEEE Trans. Ind. Electron., vol. 58, no. 4, pp. 1294–1306, Apr. 2011.

- [9] S. Ding, M. Cheng, Z. Wang, K. T. Chau1, Y. Wang, and W. Wang, "A hybrid-source switched-capacitor multilevel converter for electric vehicles," in Proc. ICEMS, Incheon, South Korea, 2010, pp. 288–292.

- [10] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A survey on cascaded multilevel inverters," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2197–2206, Jul. 2010.

- [11] M. F. Kangarlu and E. Babaei, "A generalized cascaded multilevel inverter using series connection of sub multilevel inverters," IEEE Trans. Power Electron., vol. 28, no. 2, pp. 625–636, Feb. 2013.

- [12] K. N. V. Prasad, G. R. Kumar, T. V. Kiran, and G. S. Narayana, "Comparison of different topologies of cascaded H-bridge multilevel inverter," in Proc. ICCCI, Odisha, India, 2013, pp. 1 6.

- [13] C. M. Young, N. Y. Chu, Y. C. Hsiao, and C. Z. Li, "A single-phase multilevel inverter with battery balancing, "IEEE Trans. Ind. Electron., vol. 60, no. 5, pp. 1972–1978, May 2013.

#### **BIOGRAPHY**

Yadam Nagendra received B.Tech degree from Kandula Obul Reddy memorial College of Engineering (JNTUA) in the year 2012 and received M.Tech in the stream of Power Electronics at St.Martin's Engineering college (JNTUH) in the year 2014. Currently working as a Assistant Professor in Narsimha Reddy Engineering college for two years. His current research interests include power electronics for photovoltaic (PV) applications and PV generation and monitoring, include multilevel converters, power converters for distributed energy resources.

**R. KUMARA SWAMY** received B.Tech degree from Balaji Institute of Technology and Science (JNTUH) in the year 2011 and received M.Tech in the stream of Power Electronics at CMR College of Engineering and Technology (JNTUH) in the year march 2014. Currently working as a Assistant Professor in **Narsimha Reddy Engineering College** for three years. And his areas of interest are Applications of Power electronics in "Power Systems& Electrical machines".